Types of PCB Vias

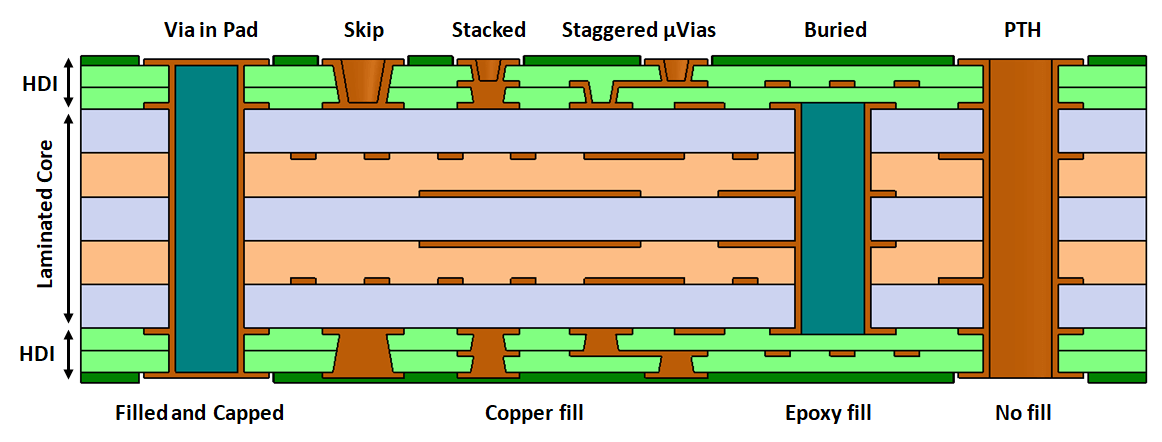

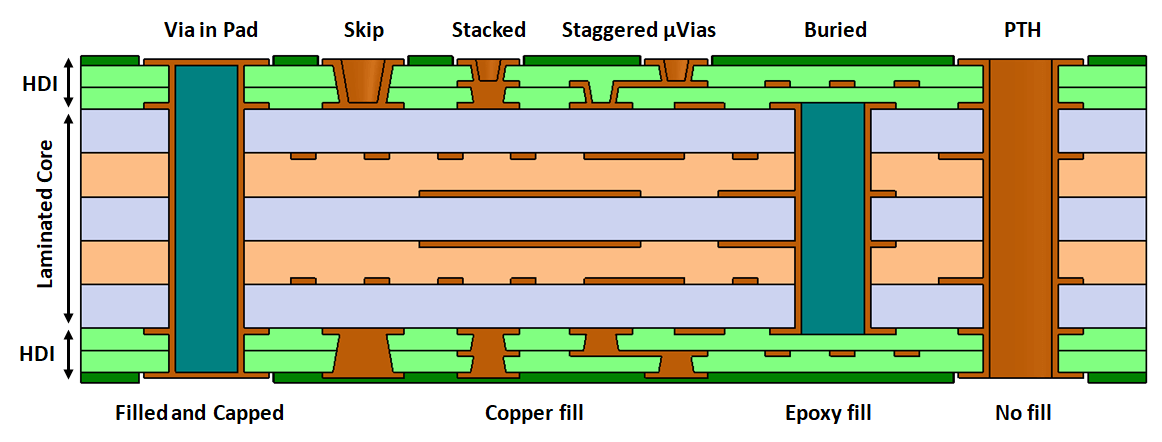

FIG. 1 - Types of PCB vias

FIG. 1 presents quite a complex 10 layer HDI construction PCB with different kinds of vias. Let's go over this as an introductory and explain different concepts and also review some terminology used in the PCB world. For this tutorial, let's assume FR-4 materials only, this means cores and prepregs which are based on woven glass and epoxy.

HDI PCB Construction

HDI stands for

high density interconnect, this construction involves multiple stages of lamination under the heat press and usually also multiple stages of drilling and plating (whereas regular multilayer board usually involves only one stage each of lamination, drilling, and plating). As such, this is a costly process and usage of features like via types, their filling, plating, and layer to layer drilling - should all be done with great care and understanding of the fabrication steps. Basically, you pay for the processes required and your objective is to find the best fit construction for the application requirements.

For interesting HDI build pictures, please refer to

[4].

Microvia

HDI goes hand in hand with the microvia which is a laser-drilled plated hole that usually spans two layers only. The microvia is smaller than the standard plated through via, or PTV for short. As a rule of thumb, a 20/10 mil PTV is four times more area consuming than a 10/4 mil microvia - therefore the potential of space savings on the top and bottom component layers is significant.

In addition, because the PTV is a multilayer constraint, on a high layer count board the PTV consumes a lot of board space - little on each of the layers of the stackup, while the microvia only consumes area on the two copper layers it designed on. The HDI construction secret powers are all about eliminating as many PTVs as possible and the freedom to move the remaining ones to more convenient locations.

Stacked and Staggered Microvias

Stacked microvias are microvias that are designed on top of each other. They allow an electrical connection spanning more than one dielectric layer and at the same time maintain the small size of the standard microvia (as opposed, for example, to a skip via that must increase in size). In this configuration, copper filling (or less common, via capping) is required for all the microvias of the stack except for the outermost via, the same as a building having structural columns on each floor, here the copper filing is used for electrical connection between the microvias in the stack.

Staggered microvias offer an alternative construction in which the microvias are designed next to each other, like a stairway. Essentially these vias are designed as simple one-layer microvias and there is no need for via filling which is a time consuming and costly process.

The staggered microvias are considered more cost effective to produce and more reliable

[7] than stacked microvias, however, from a signal integrity perspective the stacked configuration is better because of shorter connection path has lower parasitic inductance and capacitance.

Skip Via

Also called skip microvia, this is a special type of microvia that is designed to skip one copper layer and is usually designed from the outer layers. In FIG. 1 there are skip via from L1 to L3 and from L10 to L8.

The skip via can potentially save one drilling and one plating operation in the HDI PCB construction (as compared to stacked and staggered constructions) - if designed correctly and in case no other elements in the board require them.

However, these vias must be made larger than standard one-layer microvias because the plating of this via is more difficult to produce. In an attempt to reduce the size of the skip via, the PC designer might want to lower the prepreg thicknesses of the involved layers (i.e 1-2 and 2-3 prepregs) but this causes an additional constraint not previously required. This, in turn, might cause problems with impedance matching of traces with a very close plane layer.

Lastly, many manufacturers might not be as skilled in this process and may opt to change the design and quote their price based on a stacked microvia construction. This means that you might not get the cost benefit from this construction but you still 'paid' for the bigger via size in your PCB design.

Laminated Core

HDI board starts its fabrication as an ordinary multilayer board, referring in the figure above to the central laminated core. In comparison, the production of a regular board (non-HDI) only includes some final stages compared to the laminated core, these are the solder mask, surface finish (i.e ENIG, HASL, OSP, etc), and silkscreen. So we can think of the laminated core as a regular board that is missing some final processes.

The Laminated core involves a single heat pressing stage of cores and prepregs. The core (also called C-stage laminate or CCL - copper-clad laminate) comes as a sheet of woven glass fibers fully cured in epoxy and having copper foils attached on both sides (usually). In the figure above there are 3 cores seen as gray purple sheets. the manufacturer will etch away copper from all cores on both sides except for the outer layers of the laminated core, which will be etched only after plating the buried vias since the outer layers are needed for conduction of current during the copper plating process of the vias.

The prepregs, also called B-stage laminate, are sheets of woven glass fibers partially cured in epoxy (hence the name B-stage, to represent that additional curing is necessary). In the figure above we have 2 prepreg layers in light brown in between the 3 core sheets. The entire structure is then heat pressed to form the laminated core and then drilled and plated.

Buried Via

The buried via is drilled into the laminated core and as its name suggests, it will be later covered by additional layers of the PCB (the sequential buildup). Because of this reason, the buried via will usually be filled with epoxy so that there will not be open holes that can suck material from additional layers in the build. The buried via is mechanically drilled and the construction and clearances applied to regular multilayer vias are the same for the buried via.

Sequential Buildup

In the figure above, two layers are added from each side of the laminated core. This is referred to as sequential build since they are heat pressed in two additional stages after the laminated core has been prepared. In the first stage, the two inner layers are pressed to the top and bottom of the laminated core and in the second stage, the two outer layers of the PCB are added. In between these stages, there may be additional drilling and plating, that is highly dependent on the HDI construction and the types of vias designed.

PTH - Plated Through Hole

There is some ambiguity with the term PTH as some regard this as a via and some as other through holes. The PTH can mean both because any hole which is plated and going through all the layers in the board is a PTH, for examples holes for fitting a connector pin in which the lead is inserted and soldered to the hole. Via can also be a PTH but in this case, it will be better termed PTV - plated through via, this resolves any ambiguity with naming. Please also note that the term PTH is often used with an emphasis on the hole being plated while in contrast, the term NPTH emphasizes that the hole is not plated.

Via in pad (IPC 4761 type 7)

Also called VIPPO, this is one of the most interesting technologies. As the name suggest this via is allowed to be placed directly under pads of components on the board and as such the pad shape is not always round. Regular PTV must not be located on component pads because there is a problem of solder that can flow down the via's barrel and weaken the joint with the component's lead. However, the via in pad is fully shut and so solder wicking down the barrel is not a problem.

Basically, the via in pad is a through hole via which had its hole filled with epoxy or other conductive paste, then excess material is scraped from the outer surfaces to flatten it, and finally, the openings on top and bottom are plated over with copper. It is a costly operation that can add up to 20% to the board cost - since it involves many additional fabrication processes.

By the way, this via has way too many names which all refer to the same structure - sometimes called VIPPO, short for Via In Pad Plated Over, sometimes called filled and capped via, the standardized IPC name is IPC-4761 type 7, and the street name in china factories is just 'resin hole' (we don't recommend using this name as it's ambiguous). If you decided to use this type of filling make sure the manufacturer understands your requirement since there are other via filling options like plugging and tenting - so please be accurate in the fab notes documentation. Second, once this structure is decided, to lower costs it is better to specify all your PTV as VIPPO and avoid separate sets of constructions because this can add even more fabrication steps.